ASML планирует широкое применение технологии High‑NA EUV уже в следующем году для производства чипов с размером транзисторов 1,4 нм и менее.

Краткое содержание

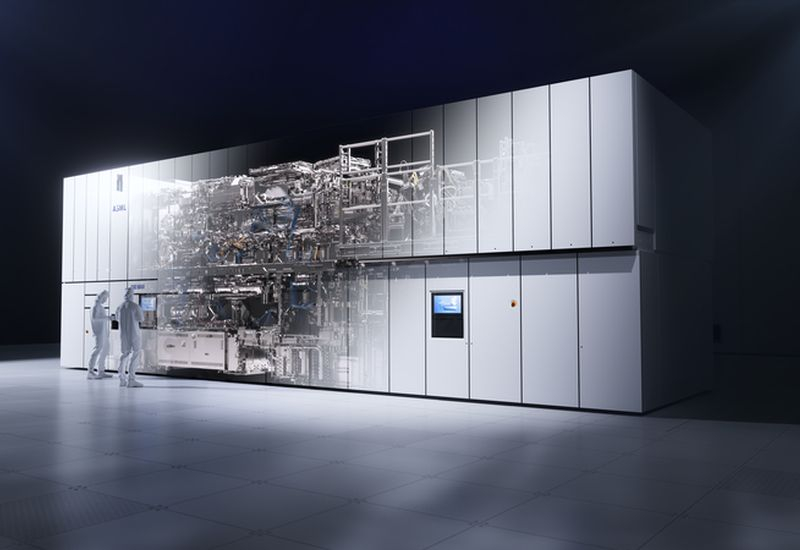

Новый этап миниатюризации микросхем требует перехода к более продвинутым методам литографии. В ближайшие два года отрасль должна запустить производство чипов с использованием оборудования класса High‑NA EUV, которое позволяет достичь размеров до 8 нм за один проход и открывает путь к техпроцессам 1,4 нм и менее 10 нм (DRAM).

1. Технологические возможности High‑NA EUV

| Параметр | Значение |

|---|---|

| Числовая апертура (NA) | 0,55 |

| Минимальный размер за один проход | ≤ 8 нм |

| Возможные техпроцессы | 1,4 нм (интегральные микросхемы), < 10 нм (DRAM) |

Эти характеристики делают оборудование ASML Twinscan EXE:5200B и аналогичные решения критически важными для будущих микроэлектронных технологий.

2. Ключевые игроки

| Компания | Статус внедрения | Комментарий |

|---|---|---|

| ASML | Производитель High‑NA EUV | Первые клиенты: Intel, Samsung, SK Hynix |

| TSMC | Не готов к массовому использованию | Стоимость одной системы – 380 млн USD; планируется отказ от 1,4 нм чипов |

| Intel | В декабре 2023 г. ввела Twinscan EXE:5200B | Подготовка к выпуску 14A‑технологии и сопутствующего оборудования |

| Samsung Electronics | Получила первый сканер в декабре 2023; второй – в этом полугодии | Планирует использовать его для Exynos 2600 (2 нм) и будущих Tesla‑процессоров |

| SK Hynix | Осваивает High‑NA EUV с сентября 2023 | Уже применяет обычную EUV-литографию в DRAM (10 нм), планирует использовать минимум пять слоёв EUV для 6‑го поколения |

| Micron Technology | Пока не определилась со сроками внедрения | Возможные планы по High‑NA EUV |

| Rapidus (Япония) | Осваивает 2‑нм технологию; планирует 1,4 нм в 2029 | К 2027 г. должна запустить массовое производство 2‑нм чипов на Хоккайдо |

3. Экономические аспекты

* Стоимость оборудования – одна система High‑NA EUV стоит около 380 млн USD.

* Переход к более дорогому оборудованию повышает себестоимость продукции, что в конечном итоге отражается на потребителях.

* Поэтому крупные производители (TSMC, Rapidus) проявляют осторожность и планируют внедрение поэтапно.

4. Ожидаемые сроки

Новые литографические сканеры ASML для массового производства передовой полупроводниковой продукции начнут активно применяться в 2027–2028 годах. До тех пор компании будут постепенно настраивать свои производственные линии, интегрируя High‑NA EUV в существующие технологические процессы.

Итог

Переход к High‑NA EUV – ключевой шаг для достижения размеров до 1,4 нм и более компактных DRAM. Крупнейшие мировые игроки уже начали подготовительные работы, но массовое внедрение ожидается только через несколько лет из‑за высоких затрат и необходимости адаптации производственных цепочек.

Asted Cloud

Asted Cloud

Комментарии (0)

Оставьте отзыв — пожалуйста, будьте вежливы и по теме.

Войти, чтобы комментировать